이전 포스트에서는 Multi-bit CDC(Clock domain Crossing)의 해결책 중에 하나로 2-bit 신호를 1-bit 신호로 만들어서 전송하는 예제에 대해서 다뤘다. 그런데 항상 1-bit으로 변경할 수 있는 것은 아니다. 그러면 Multi-bit CDC를 수행할 수 있는 다른 방법을 알아보자.

Multi-bit 신호를 전달하는 데 문제점은 Multi-bit 간의 Skew로 인하여 발생하였다. 그렇다면 Clock 2 Domain에서 Multi-bit 간의 Skew가 없는 상태에서 capture 하도록 만들면 해결되지 않을 까? Multi-bit 신호의 Skew가 없다는 말은 일정 값으로 Multi-bit이 유지되고 있는 상황과 같다. Clock 2 Domain에서 일정하게 값을 유지하고 있는 상태에서 Capture를 수행하면 Skew의 문제없이 제대로 값을 가져갈 수 있다. 그러면 Clock 2 Domain에서 어떻게 Multi-bit이 일정하게 유지되는지 알 수 있을 까? Clock 1 Domain에서 Multi-bit 신호에 대한 1-bit Enable 신호를 Clock 2 Domain으로 전달하는 것이다. 1-bit Enable 신호가 Clock 2 Domain에 도착하기 까지 2-Stage Synchronizer를 거친다면, 최소 2-Cycle은 걸리고, 이때까지 Multi-bit 신호를 일정하게 유지하면 된다.

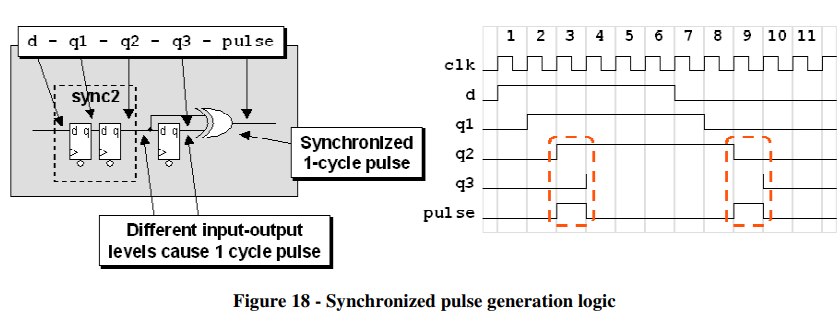

아래 그림은 1-bit Enable 신호를 전달 할 때, Clock 2 Domain에서 1-Cycle Pulse가 되도록 만들어 주는 로직이다.

이 로직을 사용하여 Multi-bit Data를 전송하는 로직을 구성하면 아래와 같다.

DataIn를 Multi-bit이라 가정하고, CDC를 수행할 때 별로의 Synchronizer를 두지 않았다. Enable 신호에만 Synchronizer를 두고, 이 신호를 통해서 Multi-bit 신호를 Capture 하였다.

Clock 2 Domain에서 Data를 계속 받을 수 있는 상황이라면 위와 같은 로직으로 구성할 수도 있다. 그런데 Clock 2 Domain이 busy인 관계로 Data를 가져갈 수 없다면, Clock 1 Domain은 이를 알고 기다려야 한다. Clock 1 Domain에서 이를 알기 위해서는 Clock 2 Domain에서 아래 그림과 같이 b_ack 신호를 전달하여 준비가 됬음을 알린다. 같은 의미로 다르게 표현하면 Clock 2 Domain에서 Clock 1 Domain으로 데이터를 요청한다고 생각할 수도 있다.

Multi-bit 신호를 전달하기 위하여 Enable 신호를 대신 CDC를 수행하였다. Enable이 Clock domain을 넘어간 시점에는 Multi-bit 신호는 Skew가 없이 Stable 한 상황이므로 Metastable 상태에 빠질 우려가 없다.

그런데, 이 방식을 사용하면 하나의 데이터를 전송할 때마다 2-Stage Synchronizer를 사용할 경우, 2-Cycle 이상 Latency가 발생한다. 전송이 완료될 때까지 기다려야 하므로 비효율적이다. 그렇다면 Synchronizer를 수행하는 Latency를 감출 수 있는 방법이 없을 까? 데이터를 쌓아두고 몇 개의 데이터가 저장되어있는 지를 Counting 하여 전달한다면, Latency를 감출 수 있지 않을 까?

이런 관점에서 다음 포스트에서는 Counter 값의 CDC를 수행하는 방법에 대해서 알아보도록 하겠다.

Reference

*[1]: Understanding Metastability in FPGAs, Altera Corporation

*[2]: Cummings, Clifford E. "Clock domain crossing (CDC) design & verification techniques using SystemVerilog." SNUG-2008, Boston (2008).

*[3]: S. Beer, J. Cox, T. Chaney and D. M. Zar, "MTBF Bounds for Multistage Synchronizers", 2013 IEEE 19th International Symposium on Asynchronous Circuits and Systems, 2013, pp. 158-165, doi: 10.1109/ASYNC.2013.18.

'IT_Study > ASIC_Study' 카테고리의 다른 글

| [CDC] 06. Gray Code vs. Binary Code(2) (5) | 2022.03.28 |

|---|---|

| [CDC] 05. Gray Code vs. Binary Code(1) (4) | 2022.03.26 |

| [CDC] 03. Multi-bit Clock Domain Crossing(1) (4) | 2022.03.19 |

| [CDC] 02. Two Flip-flop Synchronizer Usage Example (8) | 2022.03.18 |

| [CDC] 01. Metastability란 무엇인가? (0) | 2022.02.21 |

댓글